New Thermal Solver

[two-thirds]

With its new release, the well‐known 3D EM solver EMPIRE XCcel now features a novel thermal solver for the simulation of the temperature distribution of power electronics, RF circuits, integrated circuits and also including electromagnetic heating in human bodies.

The thermal simulation includes thermal conductivities of materials, surface convection and radiation cooling and supports heat sources and heat sinks for heating and cooling mechanisms.

With increasing packaging density of RF circuits heating can become a severe problem for the lifetime of critical components such as diodes (also LEDs), transistors, resistors, and ICs. Also passive structures such as filters, couplers or resonators can exhibit high currents in small areas where the temperature can rise to a critical level. In case of electromagnetic radiation the prediction of thermal heating inside of human bodies (e.g. handheld antenna attached to human head) is necessary to prevent hazards.

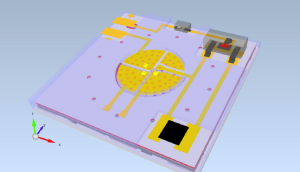

Figure 1: LTCC module with LEDs and driver circuit (click to view full size)

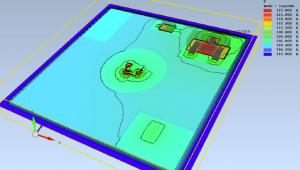

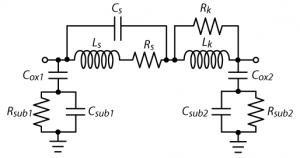

Figure 2: Temperature distribution on the LTCC module (click to view full size)

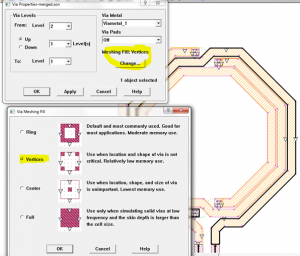

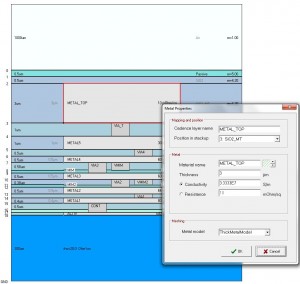

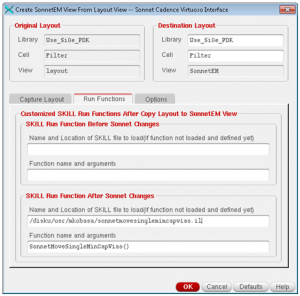

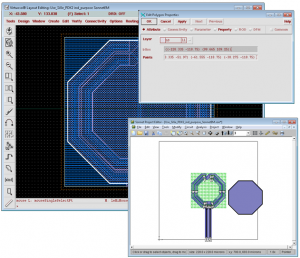

The accurate prediction of the temperature distribution is now possible with EMPIRE XCcel 6.00. The structure is created within the GUI where properties such as thermal conductivity and heat transfer rates can be entered similar as the electromagnetic properties. A large database is already equipped with known parameters. Thermal sources can be set directly, e.g. by entering a thermal power in Watt for a lumped element such a transistor. Thermal sources can be determined by an EM simulation, too. With a combined EM and Thermal simulation the RF losses are calculated in a first EM simulation run and will be used as a source for a subsequent thermal simulation. Cooling elements can be defined as surfaces with a specific thermal resistivity. In case of human body thermal modeling also the blood perfusion rate can be taken into account. In addition, known thermal properties are available in a tissue data base.

The simulation engine automatically identifies the surface to air interfaces and invokes the heat transfer mechanisms such as radiation and convection. With this method, cells filled with air don’t need to be part of the solution thus minimizing the number of cells to be simulated for the temperature distribution. A robust and efficient solver kernel is used for the fast solution of the thermal equations. An adaptive scheme optimizes the over‐relaxation factor during the iteration process for maximum simulation speed. After simulation the temperature distribution can be displayed together with the structure. The temperature can be displayed as distinct planes, as maximum or minimum of each plane or as top‐ and bottom side temperature distribution. The latter is especially intended for the comparison with infrared camera pictures.

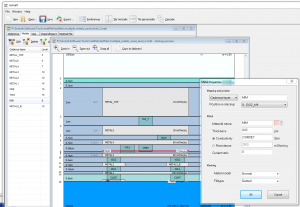

As an application example an LTCC module is shown in Figure 1 which has been developed in a joint project of the German companies odelo LED GmbH, IGOS GmbH and IMST GmbH and was co‐funded by the German federal state North Rhine Westphalia (NRW) and the European Union (European Regional Development Fund: Investing In Your Future). It contains 3 LED chips on top which are die‐ and wire‐bonded to the top metallization. A small driver circuit with Shottky diode, transistor and resistor is placed on top side, too. Many thermal vias are integrated beneath the active elements to transfer the heat from the topside to the heatsink at the bottom side. In this case the power loss is known and entered as lumped and distributed heat sources.

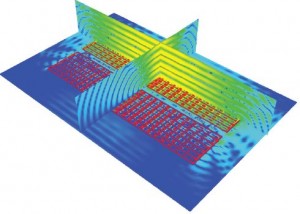

Figure 2 shows the topside temperature distribution obtained with EMPIRE XCcel 6.00. The module is subdivided into 10.3 million cells and an accuracy of 0.6 mK has been obtained after 2700 iterations. The simulation time needed is about 3 minutes on a Notebook with Intel Core i7‐2620M CPU @ 2.7 GHz. For this size the memory requirement is about 1 GByte. The temperature rise is about 40 K above ambient temperature with the maximum inside the transistor package.

As can be seen a temperature distribution for a complex structure is obtained with EMPIRE XCcel 6.00 which gives valuable input for the thermal design. As known from EMPIRE XCcel’s unique fast FDTD kernel, the new thermal solver has also been optimized with respect to solution speed thus giving reliable results within minimum of solution time.

[/two-thirds]

[third] [/third]

[/half]

[/half] [/half]

[/half]